Welcome to visit our website.

2021313 · A central aspect for operating future quantum computers is quantum circuit optimization, i.e., the search for efficient realizations of quantum algorithms given the device capabilities. In recent years, powerful approaches have been developed which focus on optimizing the high-level circuit structure. However, these approaches do not consider …

view more

The control circuit is optimized with respect to performance, power, and area, as well as design effort through interactive logic, circuit, and layout designs. The optimization scheme has been successfully applied in the design of the execution unit control and the bus controller of a 32-bit microprocessor. The tradeoffs of various design ...

view more

Silicon carbide (SiC) power modules have a wide range of applications due to their excellent electrical and thermal properties, such as high switching speed, low on-resistance, and high operating temperature. However, device reliability may suffer from overvoltage and current/voltage oscillation mainly caused by circuit parasitic inductance and capacitance. …

view more

Analog circuit design and optimization manifests as a critical phase in IC design, which still heavily relies on extensive and time-consuming manual designing by experienced experts. In recent years, the development of reinforcement learning (RL) algorithms draws attention with related techniques being introduced into the analog design field for circuit …

view more

2014122 · High power issues have become the main drawbacks of CMOS logic circuits as technology node shrinks below 45 nm. Emerging spintronics nanodevices-based hybrid logic-in-memory architecture has recently been investigated to overcome these issues. Among them, spin-transfer-torque-based magnetic tunnel junction (STT-MTJ) …

view more

2015323 · Carbon nanotube field-effect transistors (CNFETs) are promising candidates for building energy-efficient digital systems at highly scaled technology nodes. However, carbon nanotubes (CNTs) are inherently subject to variations that reduce circuit yield, increase susceptibility to noise, and severely degrade their anticipated energy and …

view more

19971113 · The relentless push for high performance in custom digital circuits has led to renewed emphasis on circuit optimization or tuning. The parameters of the optimization are typically transistor and interconnect sizes. The design metrics are not just delay, transition times, power and area, but also signal integrity and manufacturability. This …

view more

202311 · This chapter introduces seven recent machine learning (ML)-driven techniques to optimize 2D and 3D integrated circuits (ICs) implementations. The first three research articles describe the application of one such philosophy, graph neural networks (GNNs), to physical design.

view more

2009812 · This paper details the Particle Swarm Optimization (PSO) technique for the optimal design of analog circuits. It is shown the practical suitability of PSO to solve both mono-objective and multiobjective discrete optimization problems. Two application examples are presented: maximizing the voltage gain of a low noise amplifier for the UMTS …

view more

In this paper, A defected microstrip structure (DMS) design is presented for dual-band negative group delay circuit (NGDC). The frequency and group delay of each band are influenced by DMS. To promise the match of the goal frequencies, Taguchi Method (TM) is chosen to optimize the NGDC. To validate the design concept, a prototype of this NGDC …

view more

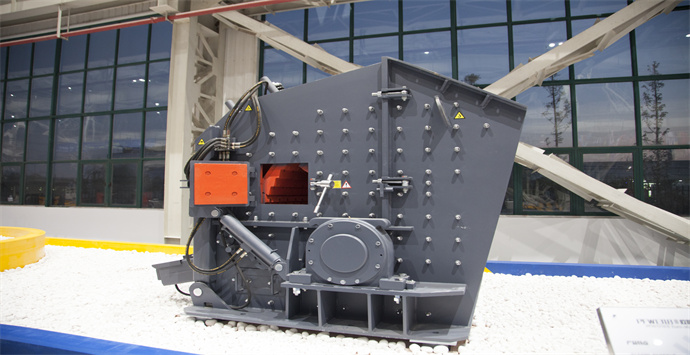

Based on over 30 years' experiences in design, production and service of crushing and s

GET QUOTE